Verilog Code for 1010 Mealy FSM Sequence Detector non-overlappingmodule mealy1010non (inp,clk,rst,y);

- Sequence Detector Examples

- Sequence Detector 1101 Vhdl Code

- Sequence Detector 1100 State Diagram

- Sequence Detector 11011 Verilog Code

- Moore State Diagram

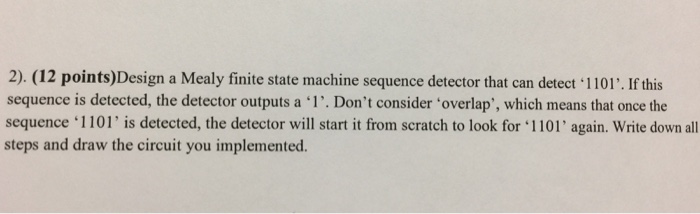

The detector with overlap allowed begins with the final 11 of the previous sequence as ready to be applied as the first 11 of the next sequence; the next bit it is looking for is the 0. Here is an overview of the design procedure for a sequential circuit. Sequence detector 1101 December 4, 2020 Leave a comment Travel Trailer Rental, Great Value Corn Starch, 16 Oz, Townhomes For Rent Woodbridge, Va, How To Tell If Bertoia Diamond Chair Is Real, Stihl Bg86c Vacuum Kit, Russian Sage Wilting, Circuits And Electronics Pdf.

/*A verilog module for 1010mealy non-overlapping FSM */input inp,clk,rst;

output reg y;

reg [1:0] current,next;

parameter first = 2'b00,

second = 2'b01,

third = 2'b10,

fourth = 2'b11;

always @ (posedge clk or posedge rst)

begin

if (rst)

current <= first;

else

current <= next;

end

always @ (current or inp)

begin

case (current)

first: if (inp 1)

begin

next = second;

y = 0;

end

else

begin

next = current;

y = 0;

end

second: if (inp 0)

begin

next = third;

y = 0;

end Star wars digital wall clock.

else

begin

next = current;

y = 0;

end

third: if (inp 1)

begin

next = fourth;

y = 0;

end

else

begin

next = first;

y = 0;

end

The average price for Energizer Batteries ranges from $10 to $30. What are the shipping options for Energizer Batteries? Some Energizer Batteries can be shipped to you at home, while others can be picked up in store. What is the top-selling product within Energizer Batteries? The top-selling product within Energizer Batteries is the Energizer. Find Batteries in all sizes, flashlights, battery chargers, supplemental power and other lighting products. Energizer: that's positivenergy!™. Energizer® Ultimate Lithium™. The #1 longest-lasting, leak-proof (based on standard use), and longest shelf-life of Energizer® AA batteries. Energizer battery charger. Energizer: Batteries. Can you imagine a day without batteries? From your watch to the remote controls, a battery powers all your essentials. One can never have too many batteries. Whether there is a power outage or you need a little extra supply, a well-charged battery always comes in handy. With everyone trying to do more with their time, a.

fourth: if (inp 0 )

begin

y= 1;

next = first;

//y = 1;

end

else

begin

next = second;

y = 0;

end

default: next = first;

endcase

end

endmodule

Sequence Detector Example

Sequence detector checks binary data bit stream and generates a signal when particular sequence is detected. The figure below presents the block diagram for sequence detector.Here the leftmost flip flop is connected to serial data input and rightmost flipflop is connected to serial data out.Clock is applied to transfer the data.Sequence generated doesn't get lost as it is fed back again as serial input to fill the register.Thus for any n bit long sequence to be generated for this configuration we need to store the sequence in an n bit shift register.

- Phone unlocking

- Digital communication system

- Remote Control

So far we have learnt the basic mechanism behind sequence detector and how it works,now let us discuss about design part.Design part sarts with input and output specification and ends with circuit diagram having sequential and combinatorial parts.Input and output specifications can be converted into state transtion diagram or ASM chart followed by state synthesis table and excitation table for flip flops and then generating design through K-map.There are two approaches for state transtion diagram

- Moore model

Sequence Detector Examples

- Mealy model

Here we will not go in details of these model as you can study from your text book or from internet but we will try to develop state transition diagram for 110 sequence detector using mealy model. State transition diagram is shown below

Sequence Detector 1101 Vhdl Code

In the above diagram input and output is in XY format respectively.The circuit is intialized with state S0,if it receives X=0 it stays at S0 else goes to S1 that indicate that first bit is detected .At S1 if it receives 1 it goes to S2 and output remains is Y=0 in both cases.In state S1 if it receives X=0 then output Y=1 hence all the three bit pattern has been received,if at state S2 X=1 then the sequence received is 111 and output Y=0.Here is the test bench for Sequence Detector

Sequence Detector 1100 State Diagram

In the above verilog code we have defined states by equivalent binary number through keyword parameter.In the design part we have used three always block.First always block does state change at positive edge of clock when reset is low.Second always block decides what will be the next state when current input and current state is provided.Third always block decides the output for input and current state. In the testbench part we have tried to test the circuit by giving X=01011001101 for 110 detection.We can view the waveform as shown below

Sequence Detector 11011 Verilog Code

In the above waveform we will get y=1 at 60 sec and 100 sec according to testbench.Here input is from right if from left ,011 detection is performed.

- Phone unlocking

- Digital communication system

- Remote Control

So far we have learnt the basic mechanism behind sequence detector and how it works,now let us discuss about design part.Design part sarts with input and output specification and ends with circuit diagram having sequential and combinatorial parts.Input and output specifications can be converted into state transtion diagram or ASM chart followed by state synthesis table and excitation table for flip flops and then generating design through K-map.There are two approaches for state transtion diagram

- Moore model

Sequence Detector Examples

- Mealy model

Here we will not go in details of these model as you can study from your text book or from internet but we will try to develop state transition diagram for 110 sequence detector using mealy model. State transition diagram is shown below

Sequence Detector 1101 Vhdl Code

In the above diagram input and output is in XY format respectively.The circuit is intialized with state S0,if it receives X=0 it stays at S0 else goes to S1 that indicate that first bit is detected .At S1 if it receives 1 it goes to S2 and output remains is Y=0 in both cases.In state S1 if it receives X=0 then output Y=1 hence all the three bit pattern has been received,if at state S2 X=1 then the sequence received is 111 and output Y=0.Here is the test bench for Sequence Detector

Sequence Detector 1100 State Diagram

In the above verilog code we have defined states by equivalent binary number through keyword parameter.In the design part we have used three always block.First always block does state change at positive edge of clock when reset is low.Second always block decides what will be the next state when current input and current state is provided.Third always block decides the output for input and current state. In the testbench part we have tried to test the circuit by giving X=01011001101 for 110 detection.We can view the waveform as shown below